| |

|

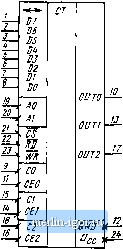

Строительный блокнот Корпуса микропроцессорных микросхем периоду частоты синхронизации сигналов, поступающих на вход RxC. Синхросигнал, поступающий на вход SYNDETjBD, может задержать начало приема информации на один период частоты синхронизации приемника из-за отсутствия правильного соотнощения во времени синхросигнала RxC и сигналов, поступающих на вход SYNDETIBD. Для исключения задержки (сдвига) бита данных, например начала приема информации по входу RxD с п-го периода частоты синхронизации сигнала RxC, необходимо на выводе SYNDETBD в период п-1 частоты синхронизации установить напряжение высокого уровня не более чем за \0Тг до начала перехода положительного полупериода сигнала RxC из состояния высокого уровня в состояние низкого уровня. Для исключения ощнбок, вызванных ложным появлением сигнала RxRDY, необходимо через два-три периода сигнала RxC после начала передачи данных произвести чтение данных без учета результата. Если в инструкции режима (см. рис. 3.7) запрограммирован синхронный прием с внешней синхронизацией, то цепи внутренней синхронизации блокируются внутренним триггером внешней синхронизации, который маскируется разрядом D6 инструкции режима и положительным фронтом сигнала RxC и устанавливается в исходное состояние прн поступлении сигнала SR или при чтении состояния микросхемы. В режиме синхронного приема с внешней синхронизацией запрограммированные синхро-символы не используются, а начало и конец приема данных определяются сигналом SYNDET/BD. Ошибки четности и переполнения контролируются тем же способом, что и в асинхронном режиме. В системах передачи данных часто необходимо контролировать то состояние микросхемы, которое устанавливается в процессе работы, сбоев, ошибок или других ситуаций Микросхема УСАПП содержит регистр состояний, позволяющий программисту читать ее состояние в любой момент времени в процессе выполнения операции. Содержимое регистра состояния не изменяется во время чтения состояния. Регистр состояний находится в буферных схемах ввода/вывода, а режим чтения производится согласно третьей строки табл, 3 10. Формат регистра состояний: SYNDETIBD Назначение сигналов DSR. SYNDETjBD, TxEND, RxRDY приведено в табл. З.Ш Исключение состанляет только сигнал состояния TxRDY разряда DO регистра состояния. Вы-вод 15 (TxRDY) маскируется сигналами CTS и Передача информации возможна разряда DO инструкции команды, а сигнал регистра состояния TxRDY не маскируется указанными выше сигналами, а только определяет, свободен или занят входной регистр данных буферной схемы ввода/вывода. Триггер ошибки стоп-бита D5 устанавливается в единичное состояние, если в конце посылки не обнаруживается стоп-бит. Триггер ошибки переполнения D4 устанавливается в единичное состояние, если микропроцессор не прочитал символ перед приемом в буферные схемы ввода/вывода новой информации. Триггер ошибки четности D3 устанавливается в единичное состояние, если в принятых данных обнаруживается ошибка Каждая из ошибок не прерывает работу микросхемы Триггеры ошибок устанавливаются в исходное состояние инструкцией команды Режим Чтение состояния позволяет использовать данную схему в системах с прерыванием и в системах с последовательным опросом внешних устройств. Максимальное время обновления информации в выходном регистре состояния буферных схем ввода/вывода происходит через период сигнала RxC Основные параметры микросхемы в диапазоне рабочих температур от -10 до --70°С и напряжении питания Ucc-5 В + 5% приведены в табл. 3.13. 3.3. Микросхема КР580ВИ53 Микросхема КР580ВИ53 - трехканальное программируемое устройство (таймер), предназначено для организации работы микропроцессорных систем в режиме реального времени Микросхема формирует сигналы с различными временными параметрами. Программируемый таймер (ПТ) реализован в виде трех независимых 16разрядных каналов с общей схемой управления Каждый канал может работать в шести режимах. Программирование режимов работы каналов осуществляется индивидуально и в произвольном порядке путем ввода управляющих слов в регистры режимов каналов, а в счетчики-запрограммированного числа байтов Управляющее слово определяет режим работы канала, 1ип счета (двоичный или двоично-десятичный), фор.мат чисел (одно или двухбайтовый). Обмен информацией с микропроцессором осуществляется по 8-разрядному двунаправленному каналу данных Максимальное значение счета, в двоичном коде 2; в двоично-десятичном коде Ю*. Частота синхронизации каналов 0-2,5 МГц. Условное графическое обозначение микросхемы приведено на рис. 3 13, назначение выводов- в табл 3 14, структурная схема показана на рис. 3.14.  Рис. 3.13. Условное графическое обозначение КР580ВИ53

Для приведения каждого канала ПТ в исходное состояние, соответствующее выбранному режиму, и для загрузки его информацией о величине счета центральный процессор (ЦП) должен выдать в ПТ некоторый набор управляющих слов и операндов. Режим работы каналов ПТ программируется с помощью простых операций ввода/вывода (табл. 3.15) Каждый из трех каналов ПТ программируется индивидуально путем записи в регистр режима управляющего слова, а в счетчик ~ запрограммированного числа байтов. Формат управляющего слова показан на рис. 3.15. Так как микросхема не имеет аппаратного вывода Начальная установка , то в

Счетчик О оито Счетчик 1 0UT1 Счетчик 2 оитг Рис. 3.14. Структурная схема КР580ВИ53 ней предусмотрен внутренний программный сброс отдельно по каналам. Сигнал внутреннего сброса формируется при записи управляющего слова в регистр режима выбранного канала. После записи управляющего слова в регистр режима выбранного канала он переводится в один из щести основных режимов работы: режим О (прерывание терминального счета); режим 1 (ждущий мультивибратор); режим 2 (генератор импульсный); режим 3 (генератор меанд- УпраШпщее слою О-дШчиый /- Яоично-дестичмий Г ежим pafomn -jtmmO 001 - ttmuM 1 XIO - режим 2 ХП - режим 3 ЮО - ретин i Ю1 - ретим 5 Чтение (заеризна) 00 - олераии ..заш1лнийания 01 - только младший байт 10 - тольно старший байт 11 - младший бвйт.звтемтарший Выбор регистра режима 00 - панал О 01 - канол I 10 - канал 2 П - заорет Рис. 3.15. Формат управляющего слова (Х-безразличное состояние) pa); режим 4 (одиночный программно формируемый стробирующий сигнал); режим 5 (одиночный аппаратно стробирующий сигнал). Диаграмма работы канала ПТ в режиме О показана иа рис. 3.16, а. В этом режиме по окончании отсчета числа, загруженного в счетчик, на выходе OUT канала ПТ усташвлива-ется напряжение высокого уровня и сохраняется до загрузюи счетчика новым значением Последовательность работы ПТ в режиме О следующая. После запнои управляющего слова в регистр режима выбранного канала на выходе OUT устанавливается напряжение низкого уровня (в режимах 1-6 - напряже- Innnnnnn СЕ OUT ппппппппп 5 J 2 г о 5 и 3 2 10 ние высокого уровня). Загрузка счетчика не изменяет состояние выхода. При подаче на вход СЕ напряжения высокого уровня включается счетчик и число, загруженное в него, де-крементируется. По окончании отсчета числа на выходе канала формируется напряжение высокого уровня. Загрузка счетчика новым числом изменяет состояние выхода - устанавливается состояние низкого уровня Перезагрузка счетчика во время счета приводит к следующему загрузка младшего байта останавливает текущий счет; загрузка старшего байта запускает новый цикл счета. В режиме О правильность загрузки счетчика мож- ппппппппппппппп СЕ\ оит\- ourV- li J 2 ! о -л г: 3 2 1 J 2 t 0 1пппппппппппппппп it 3 Z 1 0(312 I 0(3l 2 1 0(3} I I-I I-I m eu7-\ owjj 0 СП -г I r J 2 1 0(3)2 1 I I-1 1ппппппппппппппппп, OUt\oW3 2 1 0(U) 3 2 ! 0(i) 3 2 1 (n.l*)\ I-1 Г-Л I-1 I-1 , (п5) CE 0(5) и 3 2 ! 0(5)4 3 2 ! 0(5l±32 ! 0(5) I I I I I .: I r- !)Ut\ Oik) 3 2 1 0(i) 1, 3 2 I 0(i) 3 2 I 0(i) Li-I I 1 cm г; t лппппппппппппппп CE{ OUT CE \ i 3 2 ! 0 5 it 3 3 2 /0

Рис. 3.16. Временные диаграммы работы КР580ВИ53 в режиме прерывания терми нального счета (а), ждущего мультивибратора (б), генератора частоты (в), генера тора меандра (г), одиночного программного (d) и аппаратного {е) стробирующего сигнала

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||