| |

|

Строительный блокнот Корпуса микропроцессорных микросхем грузочных резисторов Лк. Расчет водится по формуле ь± : < R < 20-10-3 +Л/ / 10- UCC-2AB rt 50 10-в + УV /.10- произ- где п - число объединяемых выходов микросхем открытый коллектор ; iV--число входов, нагруженных на выходы микросхемы; IiL, /jH -входные токи низкого и высокого уровней микросхем, нагружаемых иа выход открытый коллектор . Структурная схема микро-ЭВМ на микросхемах серии КбвЗ приведена иа рис. 5.45. Глава 6 Микропроцессорный комплект серии К584 Микропроцессорный комплект серии К584 представляет собой унифицированный иабор БИС, позволяющий реализовать произвольную систему команд или структуру ЭВМ. Система команд и соответствующее программное обеспечение выбираются разработчиком в соответствии с ее назначением и реализуются микропрограммным способом. Развитая архитектура, микропрограммируе-мость и развитая система микрокоманд, широкий температурный диапазон, возможность разрядного наращивания, варьирование производительности БИС и энергии потребления Таблица 6.1

Таблица 6.2 Параметр Технология Разрядность Наращиваемость Время цикла, не Время задержки, Напряжения питания, В Ток потребления, мА

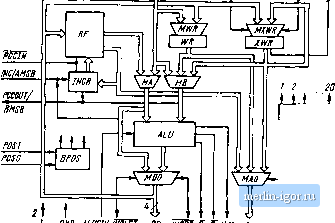

обеспечивают комплекту высокую эффективность и широкую сферу возможных применений. На основе БИС комплекта, возможно создание широкого спектра вычислителей; от простых контроллеров до универсальных микро-ЭВМ повышенной производительности. Система синхронизации всех микросхем организована по одному принципу и обеспечивает их полную логическую и временную совместимость как внутри серии Кбв4, так и с микросхемами серии К683. По всем электрическим характеристикам БИС комплекта полностью совместимы со стандартными ТТЛ-сериями. Состав комплекта микросхем серии К684 приведен в табл. 6.1. В него входят четыре БИС, выполненных по ИЛ- и ТТЛШ-технологии, с параметрами, приведенными в табл. 6.2. 6.1. Микросхема KS84BM1 Микросхема К584ВМ1 - 4-разрядная секция центрального процессора, предназначена для построения микро-ЭВМ с разрядностью. Ж IL 28 29 Рис. 6.1. Условное гра- фическое обозначение s К584ВМ1 POSf POSH ,РСШ AMSB . 0. г I о 37 Н Л /6 BMsef- Ш- Вывод Обозначение Тнп вывода Функциональное иазначеине выводов 44-47 /, 2 3-5 26, 25 20, 21, 28. 29 6 10 13 41 17, 16, 15, 14 33, 34, 36, 37 35 31, 48 24 ОРЗ-ОРО D1-D0 S2-S0 POS1-POS0 CLK DI (3)-Dl (0) WRRT WRLFT XWRRT XWRLFT XWR3J0 А LUC IN АLUCOUT PCCIN PCCOUT/BMSB INCjAMSB DO (3)-D0 (0) A3-AO Ice GND Входы Входы Входы Входы Вход (переключение фронтом) Входы Вход/выход Вход/выход Вход/выход Вход/выход Выход Вход Выход Выход Выход Вход Выход Вход, выход Выходы Выходы Вход ОР-поле слова кода операции; определяет прежде всего одну из 16 операций О-поле слова кода операции, определяет режим работы S-поле слова кода операции, определяет обычно номер выбранного регистра Определяют относительную позицию микросхемы при объединении нескольких микросхем для реализации слов длиной более четырех разрядов Тактовый сигнал, синхронизация при положительном изменении Шина данных Принимает данные при сдвиге выходных данных влево, выдает данные при сдвиге вправо Принимает данные при сдвиге выходных данных вправо, выдает данные при сдвиге влево Принимает данные при сдвиге регистра XWR влево, выдает при сдвиге вправо Принимает данные при сдвиге регистра XWR вправо, выдает при сдвиге влево Старший разряд регистра XWR в старшей позиции или младший разряд в младшей позиции Перенос в ALU Перенос из ALU Формирование переноса ALU Распространение переноса ALU Перенос программного счетчика В младшей и средней позиции выход переноса программного счетчика, в старшей позиции выход старшего разряда шины В В младшей позиции указывает программному счетчику увеличение содержимого на 2 (при наличии 1) или на 1 (при наличии 0), в старшей позиции выход старшего разряда шииы А Шина данных Шина адресов Открывает доступ программному счетчику к шине выдачи адресов Питание Общий кратной четырем, и обеспечивает хранение и арифметико-логическую обработку информации, представленной в двоичном коде. Условное графическое обозначение микросхемы приведено на рис. 6.1, назначение выводов - в табл. 6.3, структурная схема дана на рис. 6.2, формат микрокоманд показан на рис. 6.3, временная диаграмма работы приведена на рнс. 6.4. Микросхема обеспечивает все функции, необходимые для параллельной обработки 4-разрядных двоичных данных, и включает в себя: 4-разрядное арифметико-логическое устройство ALU: регистровый файл RF восьми 4-разрядных регистров общего назначения, RF7 является также программным счетчиком;  XWULFT XWRPTXWR3/o p, 6.2. Структурная схема K584BM1 RMK I- 4-разрядный рабочий регистр ffR и 4-разрядный рабочий регистр расширения блок иикрементора INCR; блок позиции BROS программируемую логическую матрицу PLA и регистр микрокоманд RMK; мультиплексоры каналов МА, MB, MWR, М XWR, MDO, МАО. Арифметико-логическое устройство микросхемы выполняет восемь арифметических операций, представленных в табл. 6.4. Операнды могут поступать на входы ALU через мультиплексоры МА, MB от входной шины DI, RF, WR или XWR. В ALU имеются схемы прчема сквозного переноса от младших разрядов ALUC1N и выработки выходного переноса ALUCOUT, выработки условия образования и распространения переноса G и Р. Эти сигналы рассчитаны иа использование схемы ускоренного переноса К166ИП4, что позволяет значительно повысить быстродействие 16-разрядиого устройства. Схемы включения БИС для расширения разрядности приведены на рис. 6.5. Результаты операций через мультиплексор MDO поступают на выход микросхемы. Промежуточные результаты могут заноситься в регистровый файл RF или в регистры WR,

XWR. Регистровая память FR предназначена для использования в качестве временной памяти для исходных данных. Последний регистр (RF7) может дополнительно использоваться в качестве программного счетчика благодаря возможности осуществлять инкремент записанного в нем кода а I или 2 с помощью внешних сигналов управления по входам INC (вывод 27) и PCCIN (вывод 212) по правилу: PCCIN=0, INC = 0, +{RF7. 1)-RF7; PCCIN = 0; INC=\\ +(RF7, 2)- RF7-PCCIN = 1 -запрет счета. Таблица 6.4

Рис. 6.3. Формат микрокоманд микросхемы К584ВМ1 * На шииу адресов выдается содержимое регистра XWR

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||