| |

Строительный блокнот Корпуса микропроцессорных микросхем

функциональное назначение выводов Передача Г-бита слова состояния процессора Передача Р-бита слова состояния процессора Контроль ошибки канала Код прерывания, йазряды 4-1 Пуск Квитирование выдачи 1 Квитирование выдачи 2 Квитирование выдачи 3 Квитирование приема Разряды 4-0 микрокоманды Синхронизация приема микрокоманды Синхронизация управляющей памяти Режим пуска процессора Общий Сброс канальный Управление запись/байт Синхронизация обмена Управление чтением данных Управление записью данных Ответ устройства Запрос на векторное прерывание Разрешение прерывания Авария источника питания Запрос радиального прерывания О Запрос радиального прерывания 3 Запрос радиального прерывания 2 Запрос радиального прерывания 1 Запрос прерывания по внешнему событию Запрос прерывания по останову Разрешение на захват магистрали Подтверждение запроса магистрали Запрос на захват магистрали Управление МПП прн выводе адреса/данных Управление МПП прн вводе данных Напряжение питания Примечание. Г - Г-бнт слова состояния процессора; Р - Р-бит слова состояния процессора; BI-B4 - разряды кода прерывания; CS - сигнал Начать ; - сигнал Исполнение ; РС/Л< - начальный пуск процессора; WTBT - признак записи/байта; INT0-INT3 - требования прерывания от внешнего устройства. К2(0}-Щ}) кт-ккщ ЕлакУП К5881У2 то-тп MMSI2 АУ H58SBC2 Ю(0}-КЮ5) СК К588ЙП упрадляющ яинии канапе e/-8i Елок МПП К5в8ВА1 mo-mi5 Сигналы 1неш-него интерфе -са /!pai<eca)pa Рнс. 8.15. Схема процессора на микросхемах К588ВГ1, К588ВУ2, К588ВС2, К588ВА1  smc тт WTIT

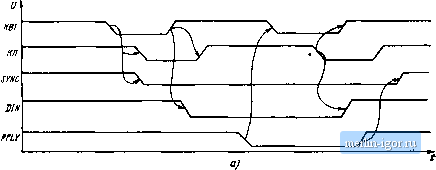

Рнс. 8.16. Временные диаграммы выполнения микрокоманд DATI (о) и DATO (б) микросхемы К588ВГ1 Условное графическое обозначение микросхемы приведено на рнс. 8.13, назначение выводов- в табл. 8.17, структурная схема показана на рнс. 8.14. Микросхема включает в себя следующие основные блоки: блок прерываний (БП); блок ввода/вывода (БВ/ВВ); блок внутреннего управления (БВУ); блок прямого доступа к памяти (БПДП); блок управления приемопередатчиками (БУП). Блок прерываний предназначен для приема запросов на обслуживание прерывания и выдачи кода прерываний в соответствии с табл. 8.18. Блок ввода/вывода предназначен для формирования на шинах ввода/вывода стандартной временной последовательности; БВУ - для формирования в микросхеме внутренних синхросигналов; БПДП-для приема запросов на захват канала прн прямом доступе к памяти; БУП - для включения и выключения канальных приемопередатчиков. Структурная схема соединения микросхем К588ВГ1, К588ВУ2, К588ВС2, К588ВА1 в составе процессора приведена на рнс. 8.15. Системный контроллер связывает внутренний интерфейс процессора с внешним интерфейсом. Внутренний интерфейс содержит линии, обеспечивающие совместную работу в процессоре: блока микросхем управляющей памяти (УП); арифметического устройства (АУ); блока микросхем магистрального приемопередатчика (МПП). Внешний интерфейс процессора содержит сигналы, обеспечивающие работу устройств Таблица 8.18

канала. Это шины ввода/вывода, прерываний и прямого доступа к памяти. Сигналы на шинах ввода/вывода SYNC, DIN. DOUT, WTBT, PRLY обеспечивают управление передачей по 16-разрядной двунаправленной шине DA0-DA15 команд, адресов, данных и векторов. Шины прерываний INTO, INTI, INT2. INT3, HALT, РОК, IRQ. lAKO, EVNT служат для приема запросов на прерывания и сброса прерываний от внешних устройств. Шнны прямого доступа к памяти DMR. DMG, SACK служат для управления предоставлением прямого доступа к памяти. Шина инициализации INIT служит для приведения внешних устройств в исходное состояние.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||