| |

|

Строительный блокнот Триггеры счетчики и регистры л л$ Л6 Л7 ЛВ Л9 милю пот лтлв ЛЗ 75 П\ 15\ 12\ 77 /0\ S[ К500ИВ160 2\ л В\ 7 8 в ЛО Л1 лг ЛЗ м J-I ЛЛ1~Лд К500ИВ1БО mi- - ло I ВЛ5 \К500АП107 i i i i ( Рис. 3.28. Схема проверки четности кода К500ИВ160: а - структура: 6 - цоколевка; в - устройство проверки 48-разрядного кода Т а б Л и ц а 3.17. Состояния схемы Таблица 3.18. Выбор режима проверки на четность К5()0ИВ160 работы для К500ИМ180

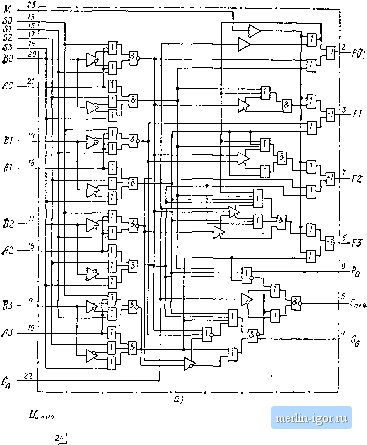

Входы выбора Режим А + В + Свх Сех + А-В Свх + В-А С ~А~В Микросхема К500ИМ180 (рнс. 3.29) содерлшт два быстродействующих двухразрядных сумматора-вычитателя. Функциональная схема одного из ннх показана на рнс. 3.29, в. Входы выбора SA и SB общие, они служат для раздельного суммирования операндов -В, >-А или вместе -А-В. Подар на эти входы логические уровни согласно табл. 3.18, можем установить один из трех режимов работы: суммирования слов А, В с приемом входного переноса Сцх, вычитания одного операнда (В или А), а также вычитания обоих операндов. Каждый операнд состоит Нз двух разрядов А1, А2 и В1, В2. Каждая поразрядная схема суммирования-вычитания имеет выходы суммы S и S, а также выход разряда переноса Свых. 21-788 V-вг- SfiO sm/sub 1 sm/sub 71 - -t>4 ULfrT4-5 1 -- / SI S2 Cg,2qj/12 B2 SB. 15\ щ щ g /7[ w\ 3\ tiBOOH/illSO 11г\з\ 1 5 6\ 7 al 52 SJ Cg,i,1Cg,1/!l .ВП/1-Щ 5) -B,2S Рис. 3.29. Сумматор-вычита-тель К500ИМ180: -структура; б -цоколевка; - схема Скорость выполнения операций велика, поскольку среднее время задержки распространения от входов операндов до выхода переноса и суммы равно 4,5 не. Время задержки от входа переноса до выхода переноса составляет 2,2 не. Микросхема потребляет ток 86 мА. Для схемы (рис. \ 3.29, е) при положительной логике выполняются уравнения: S = Cbx(AВ-f АВ) + Свх(АВ-f АВ). (3.6) Свых = СвхА-Ь СвхВ + АВ, (3.7) А =АШ8А, В =ВШ8В. (3.8) Состояния логических уровней, возможные в схеме (рис. 3.29, в), сведены в табл. 3.19. Микросхема К500ИП181 (рис. 3.30) - арифметическо-логическое устройство, по принципу действия аналогичное соответствующим микросхемам ТТЛ и КМОП (т.е. К155ИПЗ -рис. 1.130 и К564ИПЗ- рис. 2.71). Данное АЛУ выполняет 16 арифметических операций с двумя четырехразрядными словами-операндами АО-A3 и ВО-ВЗ, а также может служить генератором 16 логических функций от этих операндов. Корпус микросхемы имеет 24 вывода. Символами SO-S3 обозначены входы выбора логической или арифметической функции, которую должно выполнять АЛУ. Чтобы АЛУ выполняло арифметические операции, на вход М надо подать напряжение низкого уровня. В этом случае разрешаются внутренние пульсирующие переносы. На вывод Сп (вход сигнала быстрого переноса) также следует подать низкий уровень. Если на вход М подано напряжение высокого уровня, АЛУ геиери- рует логические функции. Сводка режимов работы АЛУ К500ИП181 приведена в табл. 3.20. Генерируемые двоичные слова выделяются на выводах F0-F3. Арифметическо-логическое устройство имеет выход сигнала быстрого переноса Сц+4, а также вспомогательные выводы Go н Ро - выходы  Т м с /!В ВО в1 й1 зг иг si sj sa; гз гг\ гу го\ ;з\ ;s\ п\ 1б\ is\ п\ гз\ пзооитв! г \ з \ t\ 5 \ б\ 1\ 8\ 9\ 10\ ll\ ti У, и1 1 п* 2 Pg ез ЯЗ §г Рис. 3.30. Арифметико-логическое устройство К500ИП181: о -схема; б -цоколевка (входы выбора SO-14, S1-17, S2-15, S3-13)

|