| |

|

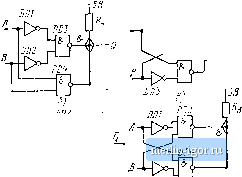

Строительный блокнот Триггеры счетчики и регистры пв1 ввг а) BBI   д) BBI да - i-1 МТ1 о ВВЗ е) BBS п 4FI, Q, Рис.- 1.35. Структуры узла исключающее ИЛИ без инверсии (а-г) и с инверсией (д-з) Если требуется многовходовой элемент исключающее ИЛИ, можно собрать его по схемам, показанным на рис. 1.36. На рис. 1.36, а дана схема трехвходового сумматора по модулю 2: Q = A©B©C, (1.5) а на рис. 1.36,6 - восьмивходового: Q = АфВфСфОфЕфРфСфН. (1.6) На .рис. 1.36, е избражена другая восьмивходовая схема, реализующая уравнение (1.6). Такая структура - основа микросхем, предназначенных для проверки на четность многоразрядных цифровых слов (см., например, рис. 1.128 и рис. 2.66). Рассмотрим несколько примеров применения микросхем исключающее ИЛИ. Выходные импульсы этих логических элементов появляются в моменты совпадения обоих входных сигналов (если оба входных уровня высокие или оба низкие). Простейший пример - устройство выделения фронта и среза входного импульса (рис. 1.37, а). Напомним, что традиционно это делали с помощью дифференцирующего CR-звена с последующим усилением п формированием сигнала. Микросхема среднего уровня интеграции исключающее ИЛИ ЛП5 илн ЛЛЗ упрощает такое устройство. Фронты выделяются здесь гораздо стабильнее. Длительность каждого выходного импульса окажется равной 31эд,р Поскольку в устройстве (рис. 1.37, а) фазы входного U вх и задержанного Ua импульсов совпадают, то в выходном элементе исключаю- Е-F- е-и- в--LJ пвг =1 - J\IJBZ ввв 1 ВВ5 =1 Е-F- н-1 Рнс. 1.36. Многовходовые элементы исключающее ИЛИ щее ИЛИ нулевое выходное иапряжение будет в двух случаях; если Uax=U3=0 и ивх=из = ии.п. Когда же Ubx==U3, выделяются выходные импульсы с длительностью 31зд,р. Другими словами, с такой точностью можно определить время прихода фронта импульса и время окончания этого импульса. Устройство, собранное по схеме (рис. 1.37, а), удваивает частоту входного сигнала. В настоящее время для преобразования оптического изображения в электрический телевизионный сигнал стали все шире применять вместо приемных электронно-лучевых трубок (например, видиконов), полупро- вт.ч 1? =7 =7 ВВП я 3 ВВ1.3 т5М5 Рис. 1.37. Устройство, выделяющее фронт и срез импульса (а), и диаграмма его работы (б) водниковые матрицы. Это микросхемы с открытой для сфокусированного изображения поверхностью, состоящей примерно из 250 тысяч светочувствительных ячеек и имеющей размер оптической зоны около 15X20 мм (число отдельных транзисторов в этой сверхбольшой интегральной схеме превышает полмиллиона!). В каждой из ячеек накапливается заряд, соответствующий яркости одной точки изображения. Все накопленные 250 тысяч зарядов при последовательном выносе их из матрицы дают кадр телевизионного изображения. Схемотехнически задача организации такого выноса весьма сложна (здесь используются специальные внешние БИС управления ячейками матрицы, связанными меж- виг KtssAos . Ш.2 пвгл

К155ЛН1 Рис. 1.38. Генератор трехфазной последовательности (а) и диаграмма его работы (б)

|