| |

|

Строительный блокнот Триггеры счетчики и регистры тм состоит из элементов DDI.2 и DD1.3. Элементы DD1.1 и DD1.4- яходиые ключи, с которых снимается сигнал С для управления ТП, защелка RS которого построена на элементах DDI.7 и DDI.8. Сигналы управления подаются на ТП через DDI.5 и DDI.6. Триггер мол<ет иметь вход общего сброса данных R, который для этой схемы иногда в литературе называют clear. Многие JK-триггеры имеют также вход предварительной установки S (другое название preset), симметричный входу R, что создает дополнительные входы у элементов DD 1.1,.DDI.2 и DDI.7. На рис. 1.49,6 показана осциллограмма переключающего импульса, на которой отмечены этапы работы составного триггера. В момент tj ТП изолирован от ТМ; в момент t2 разрешается прием данных входами ТМ. С приходом отрицательного перепада импульса в момент 1з запре-

in tnM Рис. 1.50. Триггер со входом D щается прием данных входами ТМ, а в момент t4 заканчивается перенос данных из ТМ в ТП. Таким образом, замечательное свойство двухфазного управления состоит в том, что входы приема данных за период тактового импульса, т. е. во время загрузки 1 бита информации, не имеют сквозной связи с выходными цепями. Изоляция входов и выходов обеспечивает устойчивое переключение сложного триггера, если частота тактовых импульсов нестабильна (дрожит). Наиболее часто в цифровых интегральных микросхемах, а также в импульсных устройствах применяют триггеры с единственным входом данных D (data), так называемые D-трнггеры. Одна из причин их появления была в том, что число выводов у корпусов микросхем ранних разработок не превышало 14, а стоимость ыноговыводного корпуса составляла значительную часть от стоимости готовой микросхемы. Для D-триггера требуется всего четыре вкешних вывода: вход данных D, тактовый вход С, два выхода Q и Q (один из них может отсутствовать). Схема D-триггера (рис. 1.50,а) отличается от схемы RST-триггера (рис. 1.45,6) наличием инвертора DD1.1, добавленного между входами S и R. Теперь состояние неопределенности для входов R и S исключается, так как инвертор DD1.1 формирует на входе R сигнал S. Согласно таблице логических состояний D-триггера (рис. 1.50,6) в некоторый момент времени i на вход D можно подать напряжения низкого или высокого уровня. Если в последующий момент tn-n придет положительный перепад тактового импульса, состояния на выходах Qn-n и Qn-n будут соответствовать табл. 1.50,6. На рис. 1.50,6 показаны диаграммы записи в D-триггер напряжений высокого и низкого входных уровней и их считывание. Непременное условие правильной работы D-триггера - это наличие защитного интервала времени после прихода запускающего импульса Uj-, перед тактовым (интервал времени tn-n-1 оговаривается справочными данными иа D-триггер).

Рнс. 1.51. Счетчик-делитель на 2: а - структурная схема; б - применение D-триггера для деления на 2

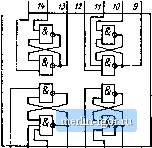

г) Q Рис. 1.52. Схемы взаимного преобразования триггеров: а -- из RS в Т; б - из D в Т; в - из JK в Т; г - Т-триггер со входом разрешения Е1; а -JK в D; е- RST в D; sic - RST в JK Если стобдить D-триггер цепью обратной связи, соединяющей выход Q со входом D, он станет работать как Т-триггер, т, е. делитель 1.:астоты в 2 раза. Действительно, нетрудно видеть, что делитель на рнс. 1,51, а по фазировке сигналов соответствует Т-трнггерному, рассмотренному на рис, 1.46, а. На рис. 1.51,6 показаны осциллограммы работы делителя на два частоты тактовой последовательности Uq. В заключение рассмотрим несколько схем взаимного преобразования триггеров. На рис. 1.52, а-в показаны схемы делителей частоты на kST-, D- н JK-триггерах соответственно. Триггер D можно преобразовать в Т (делитель на 2), снабдив делитель дополнительным входом разрешения EI (рис. 1.52, г). В режиме D-триггера можно использовать JK- и RST-триггеры (рис, 1.52,5, е). Из RST-TpHrrepa можно получить JK-триггер по схеме (рис, 1,52, ж). 1.12. RS- и D-ТРИГГЕРЫ В составе серий -ТТЛ выпускаются микросхемы, содержащие RS-, D- и JK-триггеры. Как правило, эти микросхемы многоканальные. Несколько триггеров имеют общие выводы питания и некоторые объединенные входы управления. На миоготриггерных микросхемах можно самостоятельно проектировать устройства: делители частоты, регистры, память малой емкости. KSS5TP2 58 54- 4 S3.1 S32 R3 03 1S\ г5  > Z 5 S В 7 8 r1 51,1 s1.2 q1 r2 52 32 Таблица 1.20. Состояния триггера из микросхемы К585ТР2

Рис. 1.53. Микросхема К555ТР2 Микросхема К555ТР2 (рис. 1.53) содержит четыре RS-триггера, ричем два из них имеют по два входа установки S. Для вход сброса Реактивный уровень низкий. Если на входы триггера 81, S2 и R подать одновременно напряжение низкого уровня, то на выходе Q появится напряжение высокого уровня (см, табл. 1.20). Однако это состояиие не будет зафиксировано, защелкнуто : если входные уровни Н убрать, на выходе Q появитси неопределенное состояние. При подаче на входы напряжений высоких уровней напряженне на входе Q останется без изменения. Ток потребления микросхемы К555ТР2 7 мА. Время задержки рас-

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||