| |

|

Строительный блокнот Триггеры счетчики и регистры пространения сигнала от входа S до выхода Q равно: при включении (при переходе выходного сигнала на уровень Н) 22 не, а при выключении (к уровню В) 15 не. Аналогичная задержка для входа R 27 ис (от уровня В к Н). Соответствующая зарубежная микросхема имеет наименование 74 LS 279. Микросхемы ТТЛ, содержащие наборы триггеров, перечислены в табл. 1.21. Таблица 1.21. D-триггеры ТТЛ

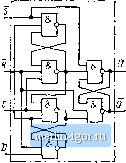

Микросхемы TM2 (рис. 1.54) содержат два независимых D-триг-£ера, имеющих общую цепь питания. У каждого триггера есть входы D, S H R, а также комплементарные выходы Q и Q (см. рис. 1.54, а). Входы S и R - асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе; активный уровень для них - низкий. Сигнал от входа D передается на выходы . m.hUBlZ  B1.Z тззтг 6)

Рис. 1.54. Два D-триггера TM2: о - структурная схема одного канала; б ~ функциональная схема; в -цоколевка Q и по положительному перепаду импульса на тактовом входе С (от Н к В). Чтобы триггер переключился правильно (т. е. согласно табл. 1.22), уровень иа входе D следует зафиксировать заранее, перед приходом тактового перепада. Защитный интервал должен превышать время задержки распространения сигнала в триггере. Если на входы S и-R триггеров ТМ2 одновременно подаются напряжения низкого уровня, состояние выходов Q и Q окажется неопределенным. Загрузить в триг-ге£ входные уровни В или Н (т. е. 1 или 0) можно, если на входы S и R подать напряжения высокого уровня. Таблица 1.22. Состояния триггера из микросхем TiH2

Асинхронная установка нужного сочетания уровней на выходах получится, когда на входы S и R поданы взаимопротивоположные логические сигналы. В это время входы С и D отключены. Функциональное обозначение триггеров микросхемы ТМ2 показано на рис. 1.54,6; ее цоколевка - на рис. 1.54, е. . Микросхемы ТМ5 (рис. 1.55) и ТМ7 (рнс. 1.56) функционально идентичны, так как обе содернот по две пары D-триггеров. Пары представляют собой простейшие защелки данных по 2 бита. Микросхемы различаются по числу выводов корпуса: микросхема ТМ5 расположена в 14-контактном корпусе, поэтому кандый ее триггер имеет только один прямой выход данных Q. Структурная схема одного D-триггера показана на рис. 1.56, S. Каждая пара триггера имеет вход разрешения за-

J £11.2 аз ВЧ

BB1.Z

ВВ13 а) £Ш

BBl.t 01 aZEI1Z-T- Q3 ш П\ 13\ й\ 11\ 10\ 9\ 8\ К155ТМ5 i\ г\ з\ Ч\ 5\ В\ 7\ 5) Л1 вг £№ вз ВЧ .30. Рнс. 1.55. Функциональная схема (а) и цоколевка (б) четырех D-трнггеров ТМ5 Of Of HZ

йгаг Q3 QJ Bf £112 nj.f mf.f W Q2 QZ Em AQ Q3 Qif m m m щ tz. 771 io\ 9\ K155TM7 /I 2\ Jl H\ - 5\ B\ 71 d\ Si m n 58 ЛУ M qf S) 1 ч> Рис. 1.56. Функциональная схема (a), цоколевка четырех D-триггеров ТМ7 (б) и схема одного D-триггера из микросхем ТМ5 и ТМ7 (в) Таблица 1.23. Состояния триггеров из микросхем TM5 и ТМ7

грузки EI1.2 и EI3.4. Когда на такой вход разрешения подается напряжение высокого уровня, данные, присутствующие иа входах D, без изменения отображаются на выходе Q (табл. 1.23). В защелке будет зафиксирована (по-другому, в ячейку памяти будет загружена) информация, имевшаяся на входе D, если состояние входа EI переключить от высокого уровня к низкому. Выход Q находится в текущем состоянии q все время, пока напряжение на входе EI остается низкого уровня. В табл. 1.23 обозначено: q - состояние Выхода Q перед приходом защелкивающего перепада на вход Е1 (от В к Н). При Е! = Н состояние входа D безразлично, D = x (т. е. на этом входи могут присутствовать или не присутствовать любые входные уровни). Микросхемы ТЛ8 и TM9 расположены в 16-контактных корпусах и Содержат наборы D-триггеров, имеющих общие входы синхрОиного

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||