| |

|

Строительный блокнот Триггеры счетчики и регистры Таблица 1.34. Режимы работы счетчика К155ИЕ4

Таблица 1.36. Режим работы счетчика К165ИЕ5

Таблица 1.35. Последовательность счета для К155ИЕ4

счета от О до 15 (т. е. последовательность смены логических уровней иа выходах Q0-Q3) будет соответствовать табл. 1.37. Другие особенности применения счетчика ИЕ5 соответствуют микросхемам ИЕ2 и ИЕ4. Микросхема К155ИЕ5 (аналог 7493) потребляет ток питания 53 мА и работает с тактовой частотой 10 МГц. Счетчик 74LS93 потребляет ток 15 мА, по входу СО максимальная частота до 10 МГц и по входу С1 до 32 МГц. Микросхемы К155ИЕ6 и К165ИЕ7 - четырехразрядные реверсивные счетчики, аналогичные по структуре. Счетчик ИЕ6 (рис. 1.67, а) двоич-  Рис. 1.66. Счетчик ИЕ5 (а) и его цоколевка (6) 90

К155ИЕ6

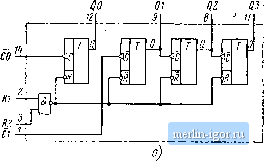

пг из <pi тп Сл-Ч{-1 КГ55ИЕ7 Сц - Q2M ГС, аз-л Р£ Си Св *4> (-1) Рис. 1.67. Счетчики ИЕ6, ИЕ7 l t l п г Q1 из а 1 7 7J из ТС а но-десятичный, а счетчнк ИЕ7 (рис. 1.67, б) - двоичный. Внутреннюю схему счетчика К155ИЕ7 можно изучить по рис. 1.67,9. На рнс. 1.67, г показана цоколевка этих счетчиков. Импульсные тактовые входы для счета на увеличение Сц (вывод 5) н на уменьшение Ср (вывод 4) в этих микросхемах раздельные. Состояние счетчика меняется по положительным перепадам тактовых импульсов от низкого уровня к высокому на каждом из этих тактовых входов. Для упрощения построения счетчиков с числом разрядов, превышающим четыре, обе микросхемы имеют выводы окончания счета на увеличение (TCjj, вывод 12) и на уменьшение (ТСр, вывод 13). От этих выводов берутся тактовые сигналы переноса и заема для последующего и от предыдущего четырехразрядного счетчика. Дополнительной логики при последовательном соединении этих счетчиков ие требуется: выводы ТСц и ТСр предыдущей микросхемы присоединяются к выводам Сц и C[j последующей. По входам разрешения параллельной загрузки РЕ и сброса R запрещается действие тактовой последовательности и даются команды загрузки четырехразрядного кода в счетчик или его сброса. В микросхемах ИЕб и ИЕ7 счетчики основаны на четырех дву.хсту-пенчатых триггерах мастер-помощник . Десятичный счетчик отличается от двоичного (см. его схему иа рис. 1.67, в) внутренней логикой; управляющей триггерами. Счетчики можно переводить в режимы сброса, параллельной загрузки, а также синхронного счета на увеличение и уменьшение. Если на вход Ср подается импульсный перепад от низкого уровня к высокому (дается команда на уменьшение-down), от содержимого счетчика вычитается 1. Аналогичный перепад, поданный на входе Сц, увеличивает (up) счет на 1. Если для счета используется один нз этих входов, на другом тактовом входе следует зафиксировать иапряжение высокого логического уровня. Первый триггер счетчика не может переключиться, если на его тактовом входе зафиксировано напряжение низкого уровня. Во избежание ошибок менять направление счета следует в моменты, когда запускающий тактовый импульс перешел на высокий уровень, т. е. во время плоской вершины импульса. На выходах ТСц (окончание счета на увеличение, вывод 12) и ТС (окончание счета на уменьшение, вывод 13) нормальный уровень - высокий. Если счет достиг максимума (цифра 9 для ИЕ6 и 15 для ИЕ7), с приходо.м следующего тактового перепада на вход Сц от высокого уровня к низкому (более 9 или более 15) на выходе ТСц появится низкое иапряжение. После возврата напряжения на тактовом входе Сц к высокому уровню иапряжение на выходе TCjj останется низким еще на время, соответствующее двойной задержке переключения логического элемента ТТЛ. Аналогично иа выходе ТСр появляется напряжение низкого уровня, если на вход С пришел счетный перепад низкого уровня. Импульсные перепады от выходов ТСцИ ТСр служат, таким дбразом, как тактовые для последующих входов Сц и Сд при конструировании счетчиков более высокого порядка. Такие многокаскадные соединения счетчиков ИЕб и ИЕ7 не полностью синхронные, поскольку на последующую микросхему тактовый импульс передается с двойной задержкой переключения.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||