| |

|

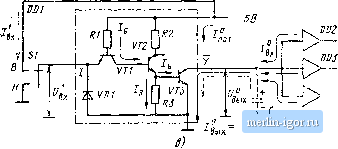

Строительный блокнот Триггеры счетчики и регистры Инвертор (рис. 1.3, г) является основой микросхем, выходы у которых имеют открытые коллекторы; он широко применяется самостоятельно. Для обозначения логической функции - инверсии применяют специальные знаки. На принципиальной схеме кружком отмечается тот вход или выход, где сигнал претерпевает переворот фазы. Черта инверсии ставится над буквенным мнемоническим обозначением данного вывода. К примеру, I - инвертирующий вход, Y -инвертирующий выход. Черта инверсии ставится и над символом команды или ее мнемоническим обозначением, например. Запись /считывание, т. е. Зп./Сч. Этим знаком отображается взаимная противоположность операций. Входы, имеющие активным входное напряжение низкого уровня 1], следует отметить знаком инверсии. На рис. 1.3, г показан импульсный усилитель с инверсией по выходу. Основная масса элементов ТТЛ снабжена двухтактным выходным каскадом (рис. 1.4, а), состоящим из выходных п-р-п-траизисторов: насыщаемого (VT5) и составного эмиттерного повторителя (VT3, VT4). Такой каскад называется квазикомплементариым в отличие от комплементарного, составленного из пары п-р-п н р-я-р-тразисторов. Транзистор р-п-р оказался неоправданно сложным технологически для цифровых микросхем. Для поочередного включения выходных п-р-п транзисторов необходим промежуточный каскад, который называется расщепителем фазы входного сигнала. На рис. 1.4, а расщепитель фазы состоит из транзистора VT2 и резисторов R2, R3. Каскад имеет два выхода: коллекторный и эмиттерный, импульсы на которых противофазны. Выходные транзисторы, включаемые поочередно, аналогичны перекидному тумблеру: иа нагрузку можно включить напряжение высокого выходного уровня, или низкого. Выход логического элемента DDI, обозначенный Y, подключается к низкому потенциалу, т. е. заземляется через насыщаемый транзистор VT6 и получает высокий выходной потенциал от эмиттера составного транзистора VT3, VT4. Инверсия входного сигнала 1 отображена на выходе символом Y. Чтобы доказать, что на рис. 1.4, а изображен инвертор, присоединим на вход I переключатель S1 (рис. 1.4,6). и подадим на его вход иапряжение низкого уровня. Транзистор VT1 не может дать базовый ток I5 транзистору VT2 (см. рис. 1.4, а), и транзистор VT2 находится в разомкнутом состоянии (на рис. 1.4, б разомкнутый транзистор VT2 условно не показан). Однако резистор R2 присоединен к проводу питания ии.п=5 В, поэтому выходное напряжение высокого уровня иых появляется на нагрузке Rh от эмиттера транзистора VT4. Статическое выходное напряжение высокого уровня для логического элемента uLx = -1 , R4 - - 2иэ- С -2) Заметим, что транзистор VT4 - эмиттерный повторитель. Он ие может перейти в состояние насыщения и поэтому минимальное напряжение усилительного режима Ujg для транзистора VT4 не падает ниже 0,7... ...1 В. Если учесть, что для транзисторов без переходов Шотки напряжение =0,7 В, получаем vljy,>(5-1-1,4) =2,6 В при стандартном напряжении питания ии.п = 5 В. Падение напряжения на резисторе R4, ограничивающем ток короткого замыкания в выходном каскаде, в первом приближении не учитываем.  Рис. 1.4. Токи и напряжения в инверторе Т1Л: а - схема инвертора; Ь - распределение токон и напряжений при низком входном логическом уровне; в - то же при высоком входном уровне R1 RZ Г\ VT3 , по Нагрузка  пап <-.- jjg Магрузк(4. Для транзисторов с переходами Шотки напряжение на р-п переходе меньше и составляет 0,2...0,3 В. Следовательно, напряжение высокого уровня Ugj для перспективных элементов ТТЛ несколько выше и достигает 3,5 В. Эмиттерный повторитель (ЭП) - усилительный каскад с отрицательной обратной связью. Следовательно, сила вытекающего эмнттерного тока будет определяться его выходным сопротивлением КвыхэП Д схемы на рис. 1.4,6 Квыхэп °2/(В-М)-Ьф./!. Здесь R2 -коллекторный резистор нагрузки транзистора-фазорасщепнтеля; (B-t-l) - полный коэффициент усиления транзистора по току. В данной схеме B=Ij/Ig для составного транзистора VT3 и VT4 определяется как произведение: В ВЗ-В4. Напомним также, что фт - температурный потенциал (фт = 26 мВ для температуры 300 К), Ijbix - вытекающий выходной ток высокого уровня логического элемента. Например, если R2 = 8 кОм, В = 1000, фт = 26 мВ, то при 1вых=5 мА, получим КвыхЭП+ ®Той сумме пересчитанный на выход номинал резистора R2, который служит сопротивлением источника сигнала для ЭП, т. е. слагаемое 8 Ом, больше, чем собственное выходное сопротивление эмиттерного перехода транзистора VT4, равное 5 Ом. На рис. 1.4,6 параллельно нагрузочному резистору Rh находится емкость Спар, символизирующая нагрузочную паразитную емкость. Для печатной платы - это погонная емкость проводящей дорожки, помноженная на ее длину. Если Сдар=100 пФ, то время нарастающего положительного перепада выходного импульса составит t = 2,2 КвыхЭппаР т. е. примерно 3 ис. Следует учесть, что поступающий от транзистора VT4 импульсный ток заряда емкости Сцар велик, однако вытекающий статический ток высокого уровня 1 мал, поскольку обслуживаемые входы последующих элементов ТТЛ имеют малые входные токи высокого уровня (см. рис. 1.3, в). В схеме на рис. 1.4,6 к выходу инвертора DDI подключен элемент-нагрузка ТТЛ DD2, на вход которого будет поступать (от эмиттера VT4) незначительный входной ток высокого уровня, т. е. ток утечки входа 1х 4х- Подадим на вход логического элемента DDI напряжение высокого уровня. Для этого в схеме на рис. 1.4, s переведем движок переключателя S1 в положение В. Транзистор-фазорасщепитель VT2 получит теперь базовый ток Ig от коллектора VT1 и поэтому откроется. Часть его эмиттерного тока Ig поступит в базу оконечного транзистора VT5. Этот транзистор перейдет в состояние насыщения, т. е. замкнется. Выходной вывод логического элемента DDI окажется подключенным к земле. Внутренее сопротивление промежутка коллектр - эмиттер г э для насыщенного транзистора VT5 реально составляет 30...50 Ом, а выходное напряжение насыщения для кремниевого транзистора UjgHac <0,3 В. Это выходное напряжение низкого уровня для элемента ТТЛ Uj. Паразитная емкость dap разряжается до низкого логического уровня через низкоомный насыщенный транзистор VT5. Длительность процесса разряда определяет время отрицательного перепада выходного импульса t°* = 2,2 ГкэСпар. Транзистор VT5 проектируется так, чтобы он мог надежно пропускать большие статические стекающие выходные токи низкого уровня вых- больше допустимое значение этого тока, тем выше нагрузочная способность элемента ТТЛ. Нагрузочную способность принято оценивать числом входов элементов-нагрузок, каждый из которых должен надежно переключиться. Учтем, что значение активного стекающего входного тока низкого уровня 1° для элемента ТТЛ велико. На рис. 1.4,8 к выходу Y присоединены три входа элементов-нагрузок DD2- DD4; если это элементы серии К155, то 1вцх = 31вх=31,6 = 4,8 мА.

|