| |

|

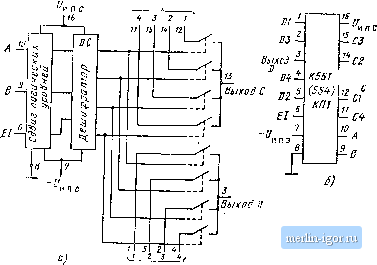

Строительный блокнот Триггеры счетчики и регистры Входы С - Выход С  Входы Л Рис. 2.29. Мультиплексор-демультиплексор К561КП1: с - схема; б - цоколевка Таблица 2.10. Управление каналами в микросхемах КП2 и КП1

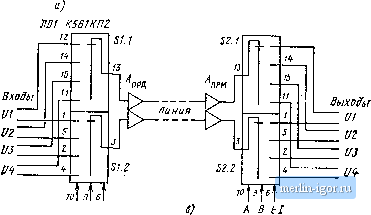

...0,28 кОм). Время задержки распространения сигнала в канале ие превышает 30 не. На рис. 2.30, а показано однополярное включение для КП1 и КП2. Согласно рис. 2.30, б, если на вывод 7 подать отрицательное напряжение питания-UjjnQ, получим возможность пропускать симметричный двухполярный аналоговый сигнал. В данном случае его амплитуда, (от пика до пика) сможет достигать ,±7,5 В, т.е. от -иэ До U nC Адресные и логические сигналы в любом из этих режимов должны иметь в качестве нуля напряжение низкого уровня. На рис. 2.30, в показан особый пример применения дифференциального коммутатора КП1. От источников U1-U4, не имеющих общей точки, сигналы через коммутатор-мультиплексор попадают на диффе> ренциальный усилитель сигналов линии, далее проходят по двухпро- КП1, КП2 IS V .n.cl5Q Ш К561КП2  А В EI Рнс. 2.30. Схемы включения К561КП1 и К561КП2; а - для коммутации однополярных сигналов; б - для коммутации двухполярныи сигналов; в - схема передачи сигналов в двухпроводную линию дифференциальным коммутатором водной ЛИНИИ связи на дифференциальный приемник и коммутатор-демультнплексор, на выходах которого последовательно получаем выборки сигналов U1-U4. Таким способом уплотняют сигналы в двухпроводной линии (здесь: четыре сигнала передаем по одной линии), 2.7. ТРИГГЕРНЫЕ МИКРОСХЕМЫ КМОП Среди микросхем КМОП присутствуют все типы триггеров: RS, D и JK (см. табл. 2.11). Наиболее популярны D-триггеры, причем в микросхемах ТМ1 и ТМ2 их содержится по два, а в ТМЗ - четыре. Микросхема TBI содержит два наиболее универсальных JK-триггера. Таблица 2.11. Микросхемы КМОП: RS-триггеры (TP), D-триггеры (ТМ) и JK-триггеры (ТВ)

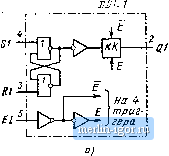

Микросхема К561ТР2 (рис. 2.31) содержит четыре RS-триггера (DD1.1 - DD1.4), что удобно для накапливания 4-разрядных двоичных слов. Выходы каждой защелки имеют третье Z-состояние. Сигнал разрешения - общий для четверки триггеров подается на вход EI. Если на этом входе нулевой уровень, выходы размыкаются (переходят в Z-состояние). Каждый триггер состоит из RS-защелки (два инвертора ИЛИ),  К561ТР2 S3 R3 Q3 az И\ 12 т -I

Qi- Ш R1 51 EI SZ. RZ -i-5) Рис. 2.31. Микросхема К561ТР2: о -схема одной RS-защелкн со входом разрешения EI; б -цоколевка

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||