| |

|

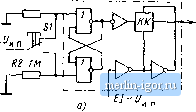

Строительный блокнот Триггеры счетчики и регистры инвертора и ключа коммутации КК (см. рис. 2.14), который управляется от шин Е и Е, объединяющих все четыре канала. Триггер имеет два входа данных R и S. Все состояния триггерного канала (рис. 2.31, а) сведены в табл. 2.12. Низкие уровни иа входах S и R не меняют состояние выхода Q. Если S=l и R=l, триггер эту информацию не защелкивает, но на выходе Q транслируется сигнал S=l (пока,он присутствует). Время задержки распространения сигнала для триггера К561ТР2 непревышает 200 не, время перехода к состоянию Z не более 100 НС. На рис. 2.32 показаны применения RS-защелок. Схема (рис. 2.32, а) позволяет устранить последствия дребезга, возникающего при переключении контакта S1, т.е. возможные ложные импульсы записи единицы в логическое устройство. При- Таблица 2.12. Состояния RS-защелки в микросхеме К561ТР2

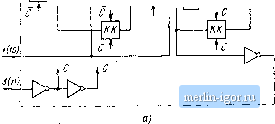

менив RS-триггер DD1.1 и двухполярный переключатель S1, получим на выходе гарантированный единственный импульс записи. На рис, 2.32, б показано устройство последовательной загрузки данных от четырех шпн данных А-D в общую, выходную. Например, по команде Загрузка В (активный уровень - низкий) данные от выбранной сейчас входной шины В проходят через четыре усилителя микросхемы DD2, фиксируются четырьмя триггерами микросхемы DD6, если на входе разрешения этой шины EIB присутствует высокий уровень. На входах разрешения EIA, EIC, ЕШ должны присутствовать низкие уровни, размыкающие выходы (следовательно, сигналы Загрузка В и Разрешение EIB должны быть инверсными). Вы.ходные сигналы передаются в четы-рехпроводиую шину через инверторы, содержащиеся в микросхеме DD9 К561ЛН2. Зафиксированные в DD6 данные можно на определенное время сохранить. Общий сброс даетси по входам R (положительный уровень). Микросхемы К176ТМ1 и К176ТМ2 показаны иа рис. 2.33. Каждая из них содержит по два D-триггера, причем триггер в ТМ1 имеет только вход сброса R, а в ТМ2 есть оба входа асинхронного управления: R и S. Структурная схема одного D-триггера показана иа рис. 2.33, а. Все состояния триггера ТМ2 сведены в табл. 2.13. Триггер переключается по положительному перепаду на тактовом входе С, прн этом логический уровень, присутствующий на входе D, передается на выход Q Входы сброса R и установки S триггера независимы от тактового входа С и имеют высокие активные уровни. Максимальная тактовая частота может достигать 5 МГц, ио время фронта тактового сигнала не должно превышать 5 мкс (см. рис. 2.7,г). С другой стороны, длительность тактового импульса должна быть более 100 не. Время установления выходных данных - более 25 не. Микросхема К561ТМЗ (рис. 2.34) содержит четыре D-триггера каждый из которых имеет индивидуальный вход D и два выхода Q и Q. Однако вход тактового импульса С общий. Кроме того, имеется общий вход переключателя полярности Р. Если на входе Р - низкий уровень, информация от входа D появится на выходе Q во время низкого уровня тактового импульса С. Если иа входе Р - высокий уровень, передача данных будет иметь место при высоком уровне на входе С. Если на входе С наблюдается перепад (положительный при Р=0 и отрицательный при Р=1), информация, присутствующая во время этого перепада на входе D, задерживается до прихода тактового импульса  1 или о Шина А Загрузка А Е1А - i 2,6.9,13 Шииа В Загрузка 8 ElB: Щз. 13 Шина С- Загрузка С Е1В= ]2,S,3,I3 Шина В- Загружав EIB ~ ]2,S,13 11, 15 Z [3,7,11.15 2 J 3,7,11,15 \3, 7, , IS BB9 KS61PH2 1 z 1 4> BDl-BB K56WES. BBS-IBB KSBITPZ Сброс /f 6) Рис. 2.32. Применение RS-защелок: a - контакт без дребезга; б -устройство загрузки данных от четырех шнн в общую SUS2] ф2) С!,[С2)  и QZ а? CZ RZ HZ >4 I n\ п\ т\ 9\ 8\ K17STM1 г Z\ 3\ 4 5\ В\ 7 В1 01 С1 R1 HI и QZ QZ сг RZ лг sz И\ 1г\ У\10\ 9\ 8\ К175ГМг 1\ 2\ 3\ 4 5\ б\ 7 S! Ql CI /f/ Л1 SI - Рис. 2.33. Микросхемы с двумя D-триггерами: о -схема одного D-трнггера; б-цоколевка К176ТЛ11; в - цоколевка К176ТМ2 противоположной полярности. Сигналы управления каждым триггером в К561ТМЗ сведены в табл. 2.14. Длительность тактового импульса должна превышать 120 ис, время хранения состояния триггера также более 120 не. Микросхемы K176TBI и K561TBJ (рис. 2.35) состоят из двух независимых JK-триггеров. Схема одного триггера представлена иа рис. 2.35, а. Триггер имеет асинхронные входы R и S, два выхода Q и Q. Данные можно подать на синхронные входы J и К согласно первым четырем строкам табл. 2.15. Сигнал, поданный на вход J или К, появится на выходах Q и Q после прихода иа тактовый вход С положительного перепада. Отрицательный перепад на входе С на информацию триггера не влияет. Последние три строки табл. 2.15 отображают действие асинхронных в.ходов S и R. Пока на этих входах присутствуют напряжения высокого уровня, на выходах Q и Q также будут напряжения высокого уровня. Максимальная тактовая частота для триггера из микросхемы К561ТВ1 составляет 3 МГц (режим Т-переключателя, делителя частоты в два раза). Длительность тактового импульса должна превышать 170 нс, однако время нарастания и спада его фронта не должно быть более 5 мкс. Длительность импульсов S и R -не менее 120 ис.

|

|||||||||||||||||||||||||||||||||||||||||||