| |

|

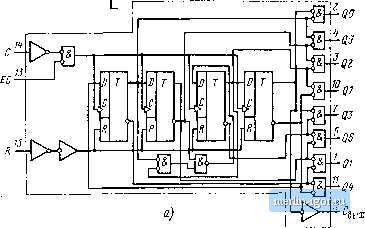

Строительный блокнот Триггеры счетчики и регистры скорости счета. При этом в выходных сигналах отсутствуют пики помех. Дешифратор переводит состояния триггера счетчика в восемь выходных, соответствующих счету от О до 7. Диаграмма высодных состояний счетчика К561ИЕ9 (рис. 2.41) сходна с диаграммой для ИЕ8 (рис 2.38) в части действия импульсов: запрет счета и сброс. Сигнал выходного переноса Свых завершает цикл счета при восьмом тактовом импульсе. Положительные фронты импульсов Свьч используются как тактовая последовательность для последующего счетчика ИЕ9. Таким образом, двухкаскадное соединеиие получается асинхронным (второй счетчик работает от пульсаций Свых), хотя каждый из счетчиков - синхронный. щ т т т ii\io\ 9\ К561ИЕЗ ТГТПтГТГТПТТГТ И1 ао аг 05. Q6 05 ~  Рис. 2.40 Счетчик-делитель на 8: о -схема ИЕЭ; б цоколевка Логические состояния и импульсные переходы счетчика ИЕЭ сведены в табл. 2.18. Длительность тактового импульса должна быть больше 250 не, поэтому максимальная тактовая частота- 2 МГц. При напряжении питания 5 В тактовая частота не превышает 0,6 МГц. При напряжении питания 15 В требуется выбрать длительность импульса сброса - более 300 ис, время его последействия составляет 275 ис (при напряжении ии.п = 5 В -- оио окажется равным 1 мкс). Схема симметричного деления интервалов на число 2<N<8 строится аналогично схеме (рнс. 2.39). Микросхема К561ИЕ10 (рис. 2.42) содержит два синхронных двоичных счетчика-делителя (без дешифраторов). Каждый счетчик основан на четырех D-триггерах (рис. 2.42, а). Линии С и ЕС (тактовая н с Jo\JnMJiШJsU6Ш Такт, Л -i - Cfpai; Запрет такта ЕС . 40 ~g~1 аэ - 01 Ш а г-IZ ff - гп Выход переноса Рис. 2.41. Диаграмма сигналов в счетчике К561ИЕ9 т{т) т{т) агНагг) азЦдзг) 7(15) I(f2) -Л -S 5(и) r1M>J н (ГалягазгтшгтЕсгсг 15\ )5\ w /Л ?г ?/ yg М KSBtHEW /I 2l Jl I 5l 1 7l Cl ECmOlQII a21Q31 Rl Рис. 2.42. Схема одного счетчика (а) и цоколевка двухканальной схемы К561ИЕ10 (б) 16-788 разрешения тактов) взаимозаменяемые, но отличаются противоположными активными уровнями, поэтому можно организовать счет по каждому фронту такта: по положительному и отрицательному. В обычном режиме на вход ЕС следует подавать напряжение высокого уровня, поэтому ход счета окажется синхронным с каждым положительным тактовым фронтом. Счетчик работает при напряжении высокого уровня на входе сброса R. Нулевые уровни на выходах Q получатся, если на входе асинхронного сброса R будет присутствовать напряжение низкого уровня. Из табл. 2.19 видно (вторая строка), что напряжение низкого уровня на тактовом входе может быть разрешающим, тогда тактовым станет вход ЕС и счетным станет отрицательный перепад импульса на входе ЕС. Таблица 2.18. Состояния счетчика К561ИЕ9 Таблица 2.19. Состояния счетчика из К561ИЕ10

Синхронные счетчики можно каскадировать, но двухкаскадная схема станет асинхронной. Для этого выход Q3 первого счетчика следует соединить со входом ЕС последующего, подав на его тактовый вход С напряжение низкого уровня. При напряжении питания ии.п=15 В максимальная тактовая частота достигает 4 МГц, минимальная длительность импульса сброса 80 НС, минимальная длительность импульса разрешения 140 не (при питании ии.п = 5 В значения этих параметров примерно в 3 раза хуже: 1,5 МГц, 250 НС, 400 не). На рнс. 2.43 показана диаграмма сигналов на выходах счетчика Q0-Q5 из микросхемы ИЕ10, где дана фазировка тактовых и разрешающих сигналов по входам С и ЕС. Восьмая линия диаграммы (рис. 2.43) показывает выходной сигнал Q3 (дес.) десятичного варианта (микросхема CD4518B) данного счетчика. Микросхема К561ИЕП (рис. 2.44) - двоичный, четырехразрядный, реверсивный счетчик. Его удобно применять для подсчета приращения данных, причем несколько корпусов ИЕН можно объединить в многокаскадные синхронные либо асинхронные счетчики. На основе этих микросхем выполняются синхронные делители частоты. Счетчик имеет

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||