| |

|

Строительный блокнот Триггеры счетчики и регистры 16, 8 и 20 мА. Наибольший ток 1, микросхемы ЛН1 потребляют, если на всех шести входах присутствуют напряжения высокого уровня. При Ubx = 4,5 в эти токи составляют 33, 66 и 54 мА для микросхем ЛН1 серий К155, К555 и К531 соответственно. Если на всех входах присутствуют напряжения низкого уровня, ток потребления 1до снижается в 2,2 раза. К155Л1П-М55ЯПЗ, К155МН5

Л Y1 К155ЛН4, niSSMfTf Рис. 1.12. Одновходовые элементы: а - инверторы ЛН1, ЛН2, ЛНЗ, ЛН5; б - буферные элементы ЛН4 и ЛП4: s - схема одного канала из ЛН4 11 YJ Микросхемы ЛН2 содержат инверторы с открытым коллектором и имеются в трех исполнениях, т.е. в составе серий К155, К555, К531. Если для стандартного варианта К155ЛН2 время 1зд,р = 55 не, то для маломощного варианта ТТЛШ К555ЛН2 оно составляет 27 не, а для скоростного К531ЛН2 уменьшается до 7,5 не. Токи потребления буферных элементов ЛН2 соответствуют микросхемам ЛН1. Микросхемы К155ЛНЗ содержат инверторы с открытыми коллекторами. У них время 1зд.р=23 не, ток потребления составляет 42 мА. Микросхемы К155ЛН4 и К155ЛП4 (рис. 1,12) состоят из шести буферных элементов без инверсии, с открытыми коллекторами. Схема одного элемента показана на рис. 1.12, е, Цоколевка микросхемы ЛП4 показана на рис. 1.12,6. Токи потребления для этих микросхем: 1пот = =30 мА, -41 мА. Максимальное время 1зд,р = 23 не. Микросхема К155ЛН5 содержит шесть буферных инверторов с открытыми коллекторами, выходное напряжение на которых можно повысить до 15 В, применив дополнительный источник питания. Таким образом, этот буферный элемент пригоден для зажигания индикаторного сегмента. По электрическим параметрам микросхемы К155ЛН5 примерно соответствует К,155ЛН4. В схемотехнике ТТЛ применяются два способа выбора по команде цифровых сигналов: разрешение по входам микросхем и по их выходам. В первом случае на время действия команды разрешается (или

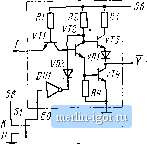

Рис. 1.13. Элементы с выводами разрешения: о -разрешение но входу EI; б - разрешение по выходу ЕО (схема с третьим Z-состоянием) запрещается) прием сигнала по входу логического элемента, во втором-выход размыкается, переходит в Z состояние. Чтобы подать на микросхему такие команды, надо предусмотреть выводы разрешения по входу EI--enable input и разрешения по выходу ЕО -enable output. Если по этим выводам управления запрещается (не разрешается) прием и выдача сигналов, их надо обозначить как инверсные EI, ЕО. На рис. 1.13, а показана схема организации входа разрешения, управляемого инверсной командой. Здесь транзисторы VT1 и VT4 имеют дополнительные, объединенные эмиттеры, которые образуют вход Е1. Если на этот вход подать напряжение низкого уровня Е1 = Н, входные токи транзисторов VT1 и VT4 через переключатель S1 будут течь на землю. Из-за этого сигнальные входы А и В никакую комбинацию напряжений высокого и низкого уровней принять не смогут. Иа выходе Q будет зафиксировано напряжение высокого уровня независимо от уровней на входах А и В. Если на входе разрешения присутствует напряжение высокого уровня Е1 = В, прохождение сигналов А и В будет разрешено. Если для проверки работы микросхемы входы А и В объединить и подать на них последовательность н.чпульсов, на выходе Q она появится в инверсной форме. На рис. 1.13,6 показана схема инвертора, который имеет третье выходное состояние Z, когда выход Q размыкается. В стандартную схему инвертора ТТЛ здесь добавлены инвертор DDI и диод VD2. Если на вход управления ЕО подать от переключателя S1 напряжение высокого уровня В, выходное напряжение инвертора DDI станет низким; катод диода VD2 будет в этот момент заземлен. Из-за этого на коллекторе транзистора VT2 окажется почти нулевой потенциал, транзистор проводить ток не сможет, нз-за чего и на резисторе R4 будет нуль падения-напряжения. Транзисторы УТЗ и VT4 при таком распределении потенциалов никакие базовые токи не получают и поэтому оба находятся в режиме отсечки, т. е. оба разомкнуты. Таким образом, выходной провод Q как бы висит в воздухе. Микросхема переходит в состояние Z с очень большим выходным сопротивлением. Если на вход ЕО подается разрешающий низкий уровень, инвертор со входом I и выходом Y работает как обычно (см. таблицу состояний на рис. 1.13,6). Логический элемент, имеющий вывод ЕО для перевода выходной цепи в состояние Z, разработан специально для обслуживания проводника шииы данных. Если к такому проводнику присоединить много выходов, находящихся в неактивном состоянии Z, то они не будут влиять друг на друга. Никаких сигналов и помех в этом проводнике не будет. Активным, передающим сигнал должен быть лишь один логический элемент, только от его выхода в проводник шины данных будут поступать единицы и нули информации. Таким образом, соединенные вместе выходы не должны быть одновременно активными.. Чтобы сигналом разрешения ЕО = Н (низкий уровень) к проводнику подключился выход только одного логического элемента, перед приходом этой команды следует предусмотреть защитный временной интервал, т. е. переключать входы ЕО элементов с паузой. Сигналы разрешения, даваемые выходам разных эле.ментов, не должны перекрываться. Недопустимы также импульсы помех на входах ЕО в момент перемены такого адреса. Чтобы защититься от таких помех, последовательность адресов ЕО удобно предварительно загрузить в регистр-накопитель (сдвиговый или с параллельным считыванием по тактовому перепаду), Для генерации последовательности адресов ЕО удобны регистры ИР8 и ИРП. Для буферного накопления адресов можно использовать микросхемы ТМ9 и ИР22. Особенность этих микросхем в том, что их выходные сигналы нарастают быстрее, чем спадают (от напряжения высокого уровня к низкому). Поскольку выходы размыкаются в состояние Z по команде ЕО=В (высокий уровень), разделение во времени сигналов выбора нужного выхода упрощается. На рис. 1.14 показаны микросхе.мы, имеющие выводы разрешения. Микросхема К155ЛП7 (рис. 1.14, а) имеет стробирование по входу EI. На рис. 1.14,6 дана схема одного канала микросхемы К155ЛП8. Здесь напряжением низкого уровня, поданным иа общий для сигнального входа и выхода вывод разрешения ЕЮ, действие входа I инвертора

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||