| |

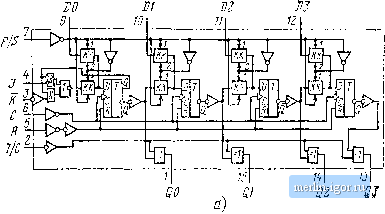

Строительный блокнот Триггеры счетчики и регистры  TicJ к f Рис. 2.53. Регистр К561ИР9 (a) и его цоколевка (б) следовательно) подано напряжение низкого уровня. Если на входе P/S присутствует напряжение высокого уровня, ключи коммутации размыкают последовательную связь триггеров, но к их D-входам подключаются линии параллельной загрузки регистра DO-D3. В случаях последовательной и параллельной загрузки информация может продвигаться по регистру согласно с положительным перепадом на так-тово.м входе С. Вход сброса R у регистра К561ИР9-асинхронный. Регистр имеет асинхронный вход Т/С, логическим сигналом на котором переключается вид выходного кода: на выходах Q0-Q3 могут быть прямой или дополнительный коды. Для получения прямого кода Т на вход Т/С следует подать напряжение высокого уровня, при напряжении низкого уровня - код дополнительный С по отношению к хранящемуся в D-триггерах. Время установления сигналов по входам J, К должно быть менее 250 НС, длительность тактового импульса большей или равной 250 не, а импульса сброса - 200 не. Микросхема К176ИР10 содержит четыре отдельных регистра (рис. 2.54). Два из ннх - четырехразрядные, два - пятиразрядные, имеющие выход и от четвертого разряда. Для всех регистров шина тактовых импульсов С - общая, однако каждый регистр имеет независимый путь данных от входов D1-D4 до выходов Q1-Q4. Данные продвигаются по регистрам в момент отрицательных перепадов тактовых импульсов. Устанавливая между выводами микросхемы перемычки, можно реализовать регистры с числом разрядов: 4, 5, 8, 9, 10, 12, 13, 14, 16, 17, 18. На рнс. 2.54, б показана функциональная схема одного D-триггера из К176ИР10. Здесь, как и в предыдущей схеме К561ИР9, используются двухтактные ключи последовательной коммутации КК; тактовые сетки С и С вырабатываются внутренней схемой. Если DDI.2 замкнут, инверторы DD1.3 и DDI.4 образуют кольцо-защелку. Регистр К176ИР10 обеспечивает сдвиг сигнала с тактовой частотой до 5 МГц. Ои удобен как основа регистрового ЗУ. JJZ- 1М> 4£l г1£1 jifU л Ш1.2 Л Л 1.3 ЛЛ14- Л1 А-А- -I /ел- /7-ri>/: -27+7 -i7+7

и.п -QZ1 KmmiQzz то Si-Z Рис. 2.54. Микросхема К176ИР10 с четырьмя регистрами (а), схема одного D-триггера (б), цоколевка ИРЮ (е) Рис. 2.55. Регистр последовательного приближения К564ИР13 (рис. 2.55) - две-последовательного использовать для Вес ао-

ail aw - St Микросхема К564ИР13 надцатиразрядный регистр приближения. Его можно построения ЦАП и АЦП на цифровой базе как КМОП, так и ТТЛ. Этот регистр может работать так же, как накопительный, либо как регистр, повторяющий одну и ту же (рутинную) управляющую программу. Регистры ИР 13 пригодны для наращивания их емкости. Они работают как в непрерывном, так и старт-стопном режимах. В схемах ЦАП резистивные матрицы R-2R можно (с некоторыми условиями) подключать непосредственно к выходагл регистра ИР13 без микросхемы аналоговых ключей. Регистр (см. рнс. 2.55) имеет тактовый выход С, последовательный вход D, куда подаются входные данные, вход разрешения регистру Е. Вход Е применяется при наращивании числа разрядов. Если оно не требуется, вход Е присоединяется к нулю. Когда на входе Е присутствует напряжение высокого уровня (1), на выходе Q11 появляется логическая 1 и преобразование запрещается. Выход Q11-прямой для старшего значащего разряда (СЗР); имеется и инверсный выход СЭР, т.е. Q11. Регистр имеет выходы каждого из 12 разрядов; от Q0 (младший ЭР) до Q11 (СЗР). Вход St - стартовый, задерживающий. Он служит для запуска цикла преобразования. Преобразование начнется, если на вход St поступит напряжение низкого уровня в момент последнего периода единицы на входе С. При этом на выходе Q11 (СЗР) появляется напряжение низкого уровня, на всех остальных (Q0- Q10) - напряжение высокого уровня. Этот момент соответствует на диаграмме (см. рис. 2.58) положительному фронту импульса 1 из тактовой последовательности С. Последовательность импульсов, поступающих на вход D (на рис. 2.58 показана последовательность, у которой чередуются высокие и низкие уровни на входе D) сихропно с тактовыми периодами, с задержкой на один период тактового импульса записываются в разряды регистра (от Q11 к Q0). На последовательном выходе данных DO входная последовательность задерживается на один период тактовой последовательности. На выходе QCC окончание преобразования отображается отрицательным перепадом (см. рнс. 2.58). Диаграмме (рис. 2.56) соответствует табл. 2.25, где перечислены все состояния на 14 периодов тактовой последовательности импульсов на входе С. Пятнадцатая строка тарл. 2.25 показывает, что при напряжении высокого уровня на входе Е преобразования запрещаются. Для запуска регистра необходимо, чтобы совпало присутствие напряжений низкого уровня на входах Е и St. В схемах АЦП на вход D поступает решение от компаратора: оставить или стереть единицу в данном разряде. При напряжении 5 В время задержки от входа С до выходов 17-788

|