| |

|

Строительный блокнот Триггеры счетчики и регистры обходима микросхема ИП4, содержащая схему ускоренного переноса СУП. Принцип действия ОЗУ можно изучить на примере матрицы 256X1 бит РУ2. Микросхема К176(К5в1)ИМ1 (рис. 2.62) - это сумматор, содержащий четыре узла поразрядного суммирования (полные сумматоры) и параллельную схему ускоренного переноса (выход Свых). Такая структура повышает быстродействие многоразрядных арифметических уз.тов, состоящих из нескольких сумматоров H-Ml. Сумматор имеет четыре BZ AZ- В1-А1 ВО-АО- I- ГУ/7

Sfix AfZ S3 АП в/з4- АГ5 - BIS 11. ft ЛЛ4- S7S {S/4. SIS \S1Z Л8 A3 A10 All Л. дых BIOJ- ,f% ВПЗ n-I 13 MX ~S11 АЛ-AS A6 47 Bfy -I- Sbix \S10 \S9 BBZ S7 \SS* 32, AO Al AZ A3

Mf-Mf-- KSSUfMf Рис. 2.62. Сумматор К561ИМ1 (a) и его цоколевка (б) Рис. 2.63. Схема суммирования двух 16-разрядных слов пары входов АО, ВО-A3, ВЗ, иа которые подаются два четырехразрядных слова А и В. От предшествующего сумматора на вход Сж можно принимать сигнал переноса. Кроме сигнала ускоренного переноса Свых, на выходе сумматора присутствуют четыре разряда суммы SO- S3. Состояния сумматора ИМ1 сведены в табл. 2.30. На рис. 2.63 по-казана схема сум.мирования двух 16-разрядных слов АО-А15 и ВО- В15. В схеме (рис. 2.64) два сумматора ИМ1 работают как преобразователь двоично-десятичного кода формата 1-2-4-8 в двоичный, сел!иразрядный. Вкодной код младшая старшая декада декада 1 г 4 8 W 20 W 80 АО ВО At В1 А2 вг A3 ВЗ К561ИМ1 S1 82 даых S3 АО ВО А1 В! AZ вг ЛЗ 83 К5Б1ИМ1 50 S1 SZ S3

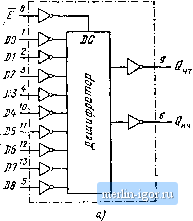

Выход двоичного кода Рис. 2.64. Сумматор К561ИМ1 в схеме преобразования кодов Время 1зд,р,ср сигнала от входов Ai, Bi к выходу Si, а также от выхода Свх до Si не более 325 не (питание 10 В). Время установления высокого или низкого уровней сигнала на выходах суммы 550 не. При напряжении ии.п==5 В значения этих временных параметров удваиваются. Микросхема CD40101B-девятиразрядное устройство проверки на четность (рис. 2.65), принимающее восьмиразрядный код DO-D7, а по девятому проводу контрольный разряд D8. Схема имеет два выхода: четный Рте и нечетный Qh,. На отдельный вход Е может подаваться сигнал запрета. При напряжении высокого уровня на входе Е оба выходных сигнала переходят на низкий уровень. Состояния на входах и выходах схемы проверки на четность сведены в табл. 2.31. Устройство применяется либо для проверки четности, либо как геяератор разряда четности. В первом случае проверяем принятое 8-разрядное слово на четность, сравнивая сумму его едщшц с конт- Таблица 2.30. Состояния сумматора К56)ИМ] Таблица 2 31. Состояния схемы проверки четности 0040101В

Рис. 2.65. Девятиразрядное устройство проверки на четность CD 40101В (а) и его цоколевка (б) рольным, девятым разрядом, во втором - передаем в линию контрольный разряд четности. Он будет сопровождать слово прн передаче, чтобы можно было проверить правильность его приема. Передавая в линию два сигнала Qt и Овч н используя на приеме входы Е н D8, можно вырабатывать сигнал запрета ошибочного слова. Время задержки распространения данных не превышает 125 не при напряжении питания Uh. =10 в (при ии.п = 5 В-400 не). Микросхема К5в1СА1-двенадцатиразрядная схема проверки на четность. В отличие от предыдущей имеет один выход Q и 13 входов (один бит - контрольный). Эта микросхема показана на рис. 2.66. По табл. 2.32 можно определить состояние выхода Q (выходные напряже-

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||