| |

|

Строительный блокнот Триггеры счетчики и регистры Таблица 2.32, Состояния устройства проверки на четность К.561СА1 Состояние входов Аа - Ац Уровень на выходе Q На всех 13 входах уровень Н На любом 1 входе уровень В На любых 2 входах уровень В На любом нечетном числе входов (<13) уровень В На любом четном числе входов уровень Н На всех 13 входах уровень В Н В Н

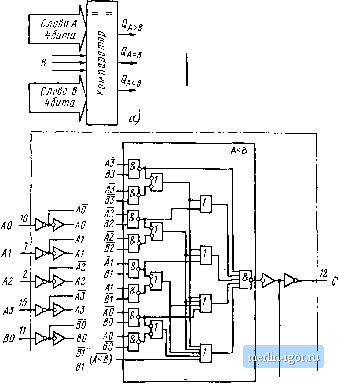

Рис. 2.66. Двенадцатиразрядная схема проверки на четность К561СА1 (а) и ее цоколевка (б) ния высокого или низкого уровня) в зависимости от четности или нечетности суммы напряжений высоких уровней. Если необходимо каскадировать две схемы К561СА1, выход первой микросхемы следует присоединить ко входу А12 второй. Микросхема К561ИП2 (рис. 2.67) - цифровой компаратор. Она сравнивает два четырехразрядных числа и имеет три выхода Qa<b, Qa>b Qa=-B отображающие неравенство или равенство двоичных или двоично-десятичных слов. Восемь входов микросхемы используются для приема входных слов АО-АЗ и ВО-ВЗ. Три входа А>В, А<В и А=В используются прн наращивании числа разрядов устройства сравнения. Если применяется только один корпус К561ИП2, на Входы А= [/и.п AJ ВЗ Ил,! d/i дв АО 51 16\ 151 1 Щ1\ Щ Щ 3\ К5В1ИПг Л г\ з\ ч\ 5\ в\ 7\ 8\i л вг Аг Q, А>В А<В А=В А1 14/  <A<g в г I-83 А>В Ч>- iA<B) {aVb) м>-

Рис. 2.67. Цифровой компаратор К561ИП2 (а), его цоколевка (б) и Полная структурная схема (в) 5 Таблица 2.33 Состояния цифрового компаратора К561ИП2

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||