| |

|

Строительный блокнот Триггеры счетчики и регистры Вход выбора функции £3 Активные - низкие уровни Логические функции (М = В) Арифметические функции (М=Н), С =Н Активные - высокие уровни Логические функции (М = В) Арифметические функции (М = Н), Сп =В

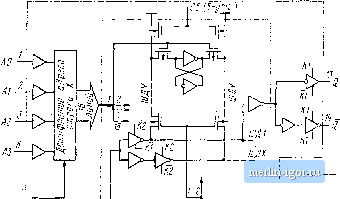

G3 G4 РЗ БЗ b tf ,X вых / гб\ >£\ п\ гз\ ?г\ 1!\ !0\ з\ ТТЛ 4 4 4 li * V2 рг GI PI G4 p/f Pg Рис, 2.71. Схема ускоренного переноса К564ИП4 (а) и ее цоколевка (б) 276 страненке переноса. На выходах СУП выполняются логические уравнения: (2.8) (2.9) (2.10) (2.11) (2.12) Сп+х = Go + Ро Сп, Cn+y = Gi + PiG + PiPoC , Cn+z = G, + P,G,+ Р, Pi Go + P, Pi Po Cn, P3P2G1 + P3P2 PiGp, GbHX = G3 + Pg G2 - Рвых = РзР2 PiPo-Время прохождения сигнала Си в СУП для Un n=15-B-125 не (400нс при t/h.n = 5B), время задержки от входов Р, G до аналогичных выходов 90 НС (300 не при иип = 5 В). Время переходного процесса 40 НС (100 НС при ии.п = 5 В).  V4> K),Z0-dblXDSbl иМатрииа , 255 Sum j All All Дешифратор адреса колонок У А5 АЗ А7 а А7 1а5 Рис. 2.72. Оперативное запоминающее устройство К176РУ2: а - схема; б - цоколевка Микросхема К176РУ2 - статическое ОЗУ, имеющее организацию: 256 слов по 1 биту, т. е. 256 ячеек хранения данных. Структурная схема этого ОЗУ показана на рнс. 2.72. В центре ОЗУ располагается матрица из 256 защелок-триггеров (показана схема одного триггера). Триггеры образуют 16 колонок и 16 рядов. Соответственно имеется 16 вертикальных и 16 горизонтальных линий управления, которые выходят из де- шифраторов адреса колонок Y и адреса строки X соответственно. Оперативное запоминающее устройство имеет восемь входов адреса. Первые четыре разряда АО-A3 выбирают адрес линии, старшие четыре - А4-А7 адрес колонки, где расположены ячейки хранения каждого одноразрядного слова. Групп а логических элементов, образующих входы CS (доступ к памяти) и R/W (Чтение/Запись), вырабатывает внутренние сигналы К2, К2 (для разрешения записи) и К1, К1 (для разрешения или запрета чтения содержимого памяти). Выводы 13 и 14 (выходы QhQ) обслуживают инверторы, имеющие состояние разомкнуто Z. Бит хранения данных вносится в память по выбранному адресу АО-А7 через вход D. Как адрес ячейки записи, так и адрес ячейки считывания выбираются в произвольном порядке. Для чтения и записи на вход CS следует подать напряжение низкого уровня. Напряжением высокого уровня на входе CS эти операции запрещаются, а выходы переходят в Z-состояние. В моменты высокого уровня на входе CS можно менять адреса ячеек (независимо от уровня на входе R/W). Вход CS в схемах, где объединяется много корпусов РУ2, служит сигналом выбора отдельного корпуса. Выходы QhQ станут активными (чтение), если на обоих входах CS и R/W уровни низкие. Если на входе R/W сменить уровень на высокий, можно записать бит информации. Сигналы управления и выходные состояния сведены в табл. 2.36. Таблица 2.36. Режим работы ОЗУ К176РУ2

Оперативное запоминающее устройство РУ2 потребляет статическую мощность 10 нВт; время выборки из памяти составляет 380 не. На вход D надо подавать напряжения высоких и низких уровней КМОП. Выходы ОЗУ могут обслуживать входы, микросхем ТТЛ. Данное ОЗУ удобно для систем с шинной структурой (имеется Z-состояние выходов, входы записи D и выходы Q, Q-раздельные). 2.12. МИКРОСХЕМЫ ФАП И МУЛЬТИВИБРАТОРЫ В дополнение к чисто цифровым среди КМОП имеются аналого-цифровые: устройство с фазовой автоподстройкой (ФАП) и ждущие мультивибраторы. Такие микросхемы позволяют упростить решение ря-

|