| |

|

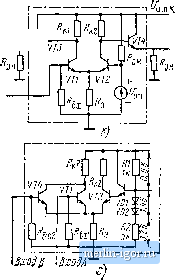

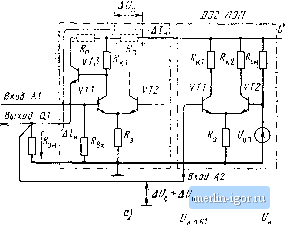

Строительный блокнот Триггеры счетчики и регистры 3. ЦИФРОВЫЕ МИКРОСХЕМЫ ЭСЛ 3.1. СХЕМОТЕХНИКА ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ Цифровые микросхемы эмиттерно-связанной логики (ЭСЛ) имеют наибольшее быстродействие, достигшее в настоящее время субнаносекундного диапазона. Особенность ЭСЛ в том, что схема логического элемента строится на основе интегрального дифференциального усилителя (ДУ), транзисторы которого могут переключать ток и при этом никогда не попадают в режим насыщения. На рис. 3.1, а показана основа логического элемента DDI-переключатель тока 1(1. -Если входным сигналом ди х открыть транзистор VT1, через него потечет весь ток 1о, вытекающий из общей точки связанных эмиттеров Э. На коллекторе транзистора VT1 окажется напряжение низкого уровня. В этот момент транзистор VT2 тока не имеет, он вынужденно находится в состоянии отсечки. На его коллекторе присутствует напряжение высокого уровня. Наличие генератора стабильного тока (ГСТ) принципиально: с его помощью строго фиксируются выходные логические уровни. В отличие от аналоговых применений дифференциального усилителя, когда стремятся использовать разность напряжений ДЦвых между коллекторами, цифровая микросхема, переключающая ток 1о, снабжа- Ьход  dbixoffff  Рис. 3.1. Исходные схемы для элемента ЭСЛ: а - дифференциальный каскад - переключатель тока; б - переключатель тока с опорным входом; s - то же с выходными эмиттерными повторителями; е - двухвходовый элемент ется двумя инверсными выходами логических уровней QhQ, где выде> ляются напряжении высокого U, и низкого U- уровней. На рис. 3.1,6 показан простейший одновходовой элемент ЭСЛ. Новым в развитии элемента DDI (рис. 3.1, а) здесь является источник опорного напряжения Uon. Это напряжение фиксирует порог срабатывания переключателя тока. Тем самым дифференциальный усилитель превращается в логический элемент. У него теперь два состояния выходов, ко. торые переключаются лишь при условиях: UBx>Uon или UDx<Uon- Однако при проектировании ЭСЛ ставилась задача: получить сверхскоростную логику. В схеме (рис. 3.1,6) этого достичь нельзя, так как выходное сопротивление выходов QhQ велико, оио приближается к номиналу Rk. Для снижения выходного сопротивления к коллекторным выходам подключаются эмиттериые повторители-транзисторы VT3 и VT4, работающие в линейном режиме (рис. 3.1, е). Теперь выходное сопротивление эмиттерного выхода принципиально уменьшается; r:Lq,-q=v(b+i). (3.1) где (В+1)-коэффициент усиления транзистора - эмиттерного повторителя по току. Эмиттерные выходы чаще делаются открытыми , чтобы можно было их соединять в элементы монтажное ИЛИ . Кроме того, внутренние нагрузочные резисторы рассеивают большую мощность, чем сильно ухудшают тепловой баланс корпуса ЭСЛ. Во многих случаях ие обязательно отбирать от повторителей VT3-VT4 максимальный ток. Сопротивление внешнего нагрузочного резистора Roh можно выбрать самостоятельно в широких пределах, например от 300 Ом до 30 кОм. На рис. 3.1, г показан следующий шаг развития схемотехники ЭСЛ: для получения нескольких логических входов следует использовать один пороговый транзистор (в схеме он составной: VT3-VT2) и несколько параллельно соединенных входных транзисторов. В данном случае логическую функцию входов А и В реализуют транзисторы VT4 и VT1. В современных ЭСЛ логические входы снабжаются внутренними резисторами утечки Rbx 50 кОм. Такой резистор, во-первых, позволяет оставлять неиспользуемые логические входы свободными, неприсоедииен-иыми; во-вторых, эти резисторы служат предыдущим элементам ЭСЛ нагрузками для их выходных эмиттерных повторителей. В правой части схемы (рис. 3.1, г) показан простейший источник порогового напряжения Uon (резисторы RT, R2 и диоды VD1, VD2), который вырабатывает опорное напряжение 4,6 В. Он снабжен эмиттерным повторителем VT3 для увеличения нагрузочной способности. Отметим дальнейшую принципиальную особенность микросхем ЭСЛ: они питаются отрицательным напряжением - Uj, (т. е. напряжение подается от эмиттеров), причем коллекторные цепи заземляются. Этим способом повышается помехоустойчивость ЭСЛ. Ток потребления 1пот вытекает из микросхемы в источник. На рис. 3.2, а показана передача сигнала Uc от эмиттерного повторителя VT3 из элемента-источника DDI (ЛЭИ) на базовый вход транзистора VT1 в логическом элементе-приемнике DD2 (ЛЭП). Видно, что большой ток потребления 1пот, протекающий по относительно тонкому проводнику коллекторного питания U j,i, имеющему определенное погонное сопротивление Rn, даст напряжение помехи AUn, которое в сумме с сигналом Uc поступит на вход А2 элемента DD2. Из этого обстоятельства следует два вывода: во-первых, коллектор- иая шина питания делается большого сечения и заземляется (дается нуль потенциала, см. рис. 3.2,6); во-вторых, разъединяются коллекторные цепи переключателя тока и эмиттерных повторителей (рис. 3.2, з). Корпус ЭСЛ имеет, таким образом, два вывода коллекторного питания -ипк! и 52 и один вывод эмиттерного - J Q = -5,2 В.  i1S 1 г/exi Вход A ..VT2 I ВьЫоЗз BbixadQ I Рис. 3.2. Способы подачи питания на ЭСЛ: а - с заземленными эмиттерами; б - с нулевой коллекторной шиной; s - с раздельными коллекторными выводами К помехам, возникающим в шнне эмиттерного питания - U д, переключатель тока - дифференциальный усилитель - менее чувствителен, так как в эмиттерной цепи присутствует генератор стабильного тока, который фиксирует ток 1о, не позволяет ему изменяться, если меняется напряжение источника эмиттерного питания - U.na (что равноценно помехе).

|