| |

|

Строительный блокнот Триггеры счетчики и регистры Ш1 -Г -г -Q

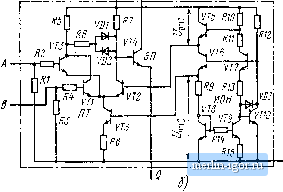

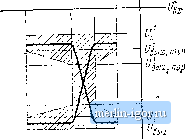

-1,Z  Рис. 3.5. Схемотехника субнаносекундной ЭСЛ: а - структурная схема логического элемента; 6 - схема переключателя тока ПТ, эмиттерного повторителя ЭП и источника опор иого напряжения ИОН; в -переключательные характеристики по выходам Q и Q нения при включении и отключении элемента, если входной импульс имеет заданную длительность фронта t * и среза t . При замерах необходимо использовать кабели и нагрузки, с сопротивлением 50 Ом. Несогласованные проводники не должны быть длиннее, чем 2 мм. К выходу схемы (рис. 3.7, а) требуется подключать вход согласованной линии передачи. При эксплуатации микросхем ЭСЛ необходимо учитывать дополнительно три временных параметра: ts-время выдержки , tt, -время хранения и tr - время сброса. На рис. 3.8, а штриховыми линиями показано, что, если на входе D данные появятся позже, чем истечет время ts. а затем поступит импульс разрешения Е, либо тактовый сигнал С, на выходе появится ошибочное напряжение низкого уровня. Uu,min bii:,max  Рис. 3.6. Диаграмма пределов переключательных характеристик элементов серии К1500 {ых, max Аналогично (см. рис. 3.8, б) информацию на входе D можно сменить после установления сигнала Е (или С) только по истечении времени хранения th- В противном случае (штриховые линии) на выходе будет отработан ложный импульс напряжения высокого уровня (а не статический низкий уровень) На рис. 3.8, в показано, что в устройствах, имеющих в.ход сброса R, перед подачей управляющих сигналов Е (или С) должен даваться защитный интервал времени tr. Здесь же показаны задержки импульсных перепадов на выходе. Многовходовые логические элементы ЭСЛ могут реализовать либо функцию ИЛИ (ИЛИ), либо И (И). На рис. 3.9,о показана схема управления переключателем тока ЭСЛ по двум входам А и В. На рис. 3.9, б показан положительный входной скачок а,в> который можно подать на вход А или В, а также отклики на него по выходам Q и Q, т. е. скачки потенциалов U и \J-. Высоким уровнем (В) здесь на- звано нулевое напряжение, низким (Н) - отрицательное выходное (О- Таблица 3.1, Входные и выходные уровни для элементов ЭСЛ

IIIJ1 эсл -60% -50% --10% -50% Рис. 3.7. Схема для измерения (а) параметров выходных импульсов (б) IoRk). Последовательно переключая напряжения уровней Н и В на вхо дах А и В с помощью переключателей S1 и S2, можем составить таблицу вы-ходных потенциалов (см. табл. 3.2). . Если назвать напряжение низкого уровня Н логическим О, а высокого В - логической 1, получим таблицу состояний ИЛИ. (сравните данные табл. 3.3 и рис. 1.15, в). Назвав напряжение низкого уровня Н логической 1, получим таблицу состояний И (вторая часть табл. 3.3). Таблица 3.2. Электрические уровни на входах и выходах схемы (рис. 3.9, а)

Таблица 3.3. Логические функции двухвходового элемента ЭСЛ (рис. 3.9, а)

Таким образом, одни и тот же элемент ЭСЛ может работать как ИЛИ (на втором выходе -ИЛИ), либо как элемент И (И). Наличие выходов Q и Q упрощает реализацию аппаратурных задач и исключает излищние задержки сигналов в дополнительных инверторах.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||